# METAMUTATOR: ITS REALIZATIONS AND ITS APPLICATIONS

ELHAM MİNAYİ

B.S. Electrical and Electronic Engineering, ISLAMIC AZAD UNIVERSITY (IAU), Tehran, 2004

M.S. Electronics and Communication Engineering, DOĞUŞ UNIVERSITY (DOU), 2014

Submitted to the Graduate School of Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electronic Engineering

> IŞIK UNIVERSITY 2019

### IŞIK UNIVERSITY GRADUATE SCHOOL OF SCIENCE AND ENGINEERING

### METAMUTATOR: ITS REALIZATIONS AND ITS APPLICATIONS

# ELHAM MİNAYİ

#### APPROVED BY:

| Prof. İ. Cem Göknar        | Işık University               |  |

|----------------------------|-------------------------------|--|

| (Thesis Supervisor)        |                               |  |

| Prof. Vedat Tavşanoğlu     | Işık University               |  |

| Prof. Serdar Özoğuz        | Istanbul Technical University |  |

| Prof. Dr. Hasan Fehmi Ateş | Istanbul Medipol University   |  |

| Assist. Prof. Merih Yıldız | Doğuş University              |  |

| APPROVAL DATE:             | //                            |  |

# METAMUTATOR: ITS REALIZATIONS AND ITS APPLICATIONS

#### Abstract

Mutators became very popular after 1971, when Leon Chua realized the memristor, his postulated fourth circuit element, using them. The reason for the popularity of mutators, which are easily realizable 2-port devices, lies in the fact that they render possible the simulation/emulation of, hence experimentation with, postulated non-existing (not off the shelf available) elements like memstors.<sup>1</sup>

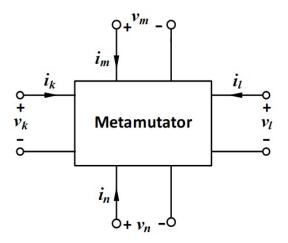

On the other hand, in the literature when simulating/emulating elements with 2-ports, many 4-port "generalized mutator-like" realizations that nobody has been able to identify are being used. These underlying 4-ports, and their ability to act as a mutator when two of the ports are properly terminated, have been thus named *metamutator*.

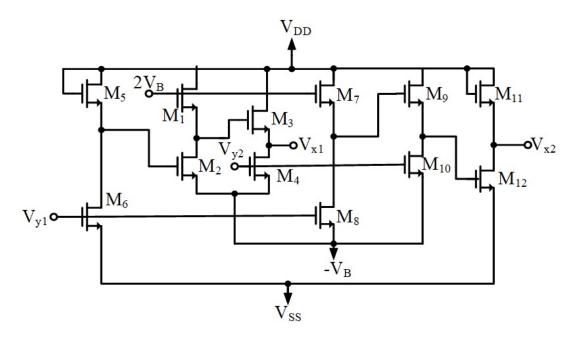

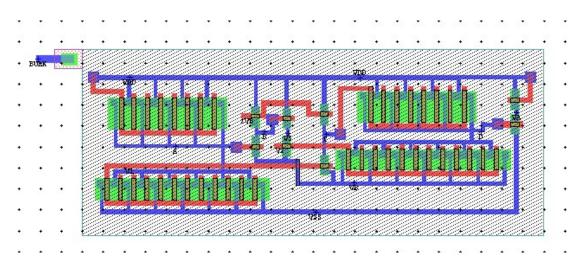

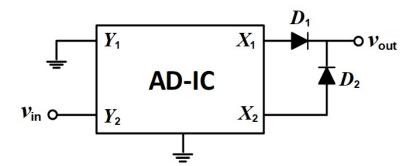

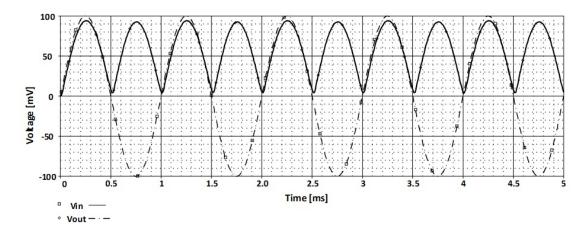

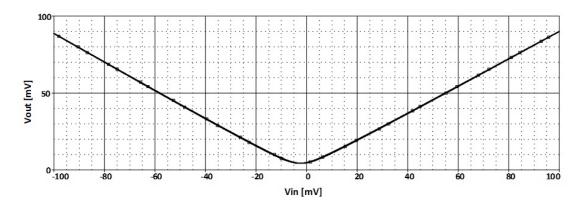

In this thesis, in addition to introducing some of metamutator realizations, newly designed metamutator circuits with one or two active devices are introduced. Also, a new active device, with only twelve transistors, named Additive and Differential IC (AD-IC), is proposed with its layout and use in metamutator circuit design. In addition, many 1-port and 2-port circuit realizations using metamutators have been introduced. 1-port applications are memstor simulation/emulation, floating and/or grounded impedance scaling which comprise inductance simulation, capacitance multiplication, oscillators and Frequency Dependent Negative Resistor (FDNR) simulation. 2- port applications cover Voltage Mode Multiple Input Single Output (VM-MISO) and Current Mode Single Input Multiple Output (CM-SIMO) universal filters and implementations of transconductance and transimpedance amplifiers. Also, two different applications of AD-IC: AD-IC based analog multiplier and AD-IC based full-wave rectifier are proposed in the thesis.

# Keywords: Mutator, memstor, memristor, metamutator, universal filter, FDNR, analog multiplier, RC-oscillator, AD-IC

<sup>&</sup>lt;sup>1</sup>Memstor is a generic name for memristor, memcapacitor, meminductor and memristance, meminductance, memcapacitance respectively.

# METAMUTATOR: GERÇEKLEMELERİ VE UYGULAMALARI

# Özet

Leon Chua'nın 1971 yılında memristorları, onları kullanarak gerçeklemesinden sonra mutatorlar ilgi odağı olmaya başladılar. Mutatorların ilgi çekmelerinin nedeni piyasada bulunmayan yeni ortaya atılmış memristor gibi, ya da bobin benzeri entegre devre teknolojisi ile uyumlu olmayan elemanların mutator devreleri kullanarak simüle/emüle edilebilmesidir.

Diğer yandan, literatürde 2-kapılılar ile elemanlar simüle/emüle edilirken, kişiler farkına varmadan çoğu zaman genelleştirilmiş mutator benzeri bir 4-kapılı yapı kullanmışlardır. Altta yatan bu gizli 4-kapılılar ve bunların iki kapıları uygun sonlandırıldığında diğer iki kapıdan mutator gibi davranmaları, metamutator adının takılmasına neden olmuştur.

Bu tezde metamutatorun, farkına varılmayan gerçeklenmeleri ve yeni geliştirilmiş bir veya iki aktif elemanlı devreleri verilmiş ve sadece on iki tranzistor kullanılarak yeni tasarlanmış bir toplayıcı ve çıkarıcı entegre devresi ile (AD-IC) bu devre tabanlı bir metamutator tanıtılmıştır.

Ayrıca metamutator kullanarak çeşitli 1-kapılı ve 2-kapılı gerçeklemeleri ile bunların birçok farklı uygulamaları tanıtılmıştır. 1 kapılı devre gerçeklemeleri ile yapılmış uygulamalara örnek olarak, endüktans simülatörü, kapasitans çarpım devresi, frekansa bağlı negatif direnç, osilatörler ve yüzer veya topraklanmış empedans dönüştürme uygulamaları tanıtılıp simülasyonları yapılmıştır. 2 kapılı olarak yapılmış uygulamalara örnek olarak: transkondüktans ve transempedans kuvvetlendiricileri, gerilim modlu çok girişli tek çıkışlı ve akım modlu tek girişli çok çıkışlı evrensel süzgeçlerin uygulamaları yapılmıştır. Ayrıca, bu tezde AD-IC tabanlı iki farklı uygulama da önerilmiştir. Birincisi AD-IC tabanlı analog çarpma devresi, ikincisi AD-IC tabanlı tam dalga doğrultucu devresidir.

Anahtar kelimeler:mutator; memstor; memristor; metamutator; evrensel filtre; FDNR; çarpma devresi; osilatör; AD-IC

### Acknowledgements

There are many people who helped to make my years at the graduate school most valuable. First of all my special thanks goes to my thesis advisor Prof. Dr. İ. Cem Göknar for his efforts, patience and guidance during this work and also sincerely thanks to Prof. Dr. Vedat Tavşanoğlu, Prof. Dr. Serdar Özoğuz and Asst. Prof. Merih Yıldız for their invaluable comments, their time and their efforts for improving the thesis.

After that thanks to my dear husband Shahram who has encouraged me for entering and helping for continuing this way by his constructive ideas during this thesis.

Also I thank my lovely daughter Aylin, who with patience has endured staying away from her mother.

And thanks my dear parents Homa and Reza and also my beloved brothers Alireza and Hamidreza, who have supported and encouraged me in all stages of life.

To

My husband Shahram

&

My parents Homa & Reza

# Table of Contents

| $\mathbf{A}$  | bstra       | $\mathbf{ct}$ |                                                             | ii   |

|---------------|-------------|---------------|-------------------------------------------------------------|------|

| Ö             | zet         |               |                                                             | ii   |

| A             | ckno        | wledge        | ements                                                      | iii  |

| $\mathbf{Li}$ | st of       | Table         | s                                                           | viii |

| $\mathbf{Li}$ | st of       | Figur         | es                                                          | ix   |

| Li            | st of       | Abbr          | eviations                                                   | xii  |

| 1             | Intr        | oduct         | ion                                                         | 1    |

|               | 1.1         | Basic         | Circuit Elements and Memstors                               | 1    |

|               | 1.2         | Litera        | ture Review                                                 | 6    |

|               | 1.3         | Gener         | alized 4-Port Mutators: Metamutators                        | 13   |

|               | 1.4         | Thesis        | s Outline                                                   | 16   |

| <b>2</b>      | Mu          | tator (       | Circuits and Memstor Simulations                            | 19   |

|               | 2.1         | Mutat         | tors for Mutating Nonlinear Circuit Elements to Memristor . | 20   |

|               |             | 2.1.1         | Mutators for Mutating Nonlinear Resistor to Memristor       | 20   |

|               |             | 2.1.2         | Mutators for Mutating Nonlinear-Inductor to Memristor .     | 23   |

|               |             | 2.1.3         | Mutators for Mutating Nonlinear-Capacitor to Memristor .    | 25   |

|               | 2.2         |               | tors for Mutating Memristor to Other Memstors               | 27   |

|               |             | 2.2.1         | Mutators for Mutating Memristor to Meminductor              | 27   |

|               |             | 2.2.2         | Mutators for Mutating Memristor to Memcapacitor             | 29   |

| 3             | <b>4-</b> P | ort M         | etamutators and Their Realizations                          | 33   |

|               | 3.1         | Incog         | nito Presence of Metamutators in Literature                 | 33   |

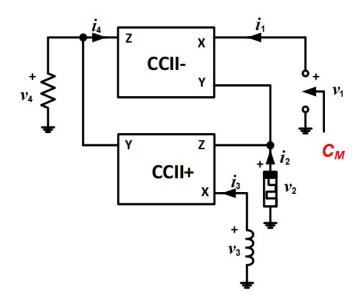

|               |             | 3.1.1         | CCII+, CCII- Based Metamutator                              | 33   |

|               |             | 3.1.2         | CCII+ and CF Based Metamutator                              | 39   |

|               |             | 3.1.3         | CCII+ Based Metamutator                                     | 43   |

|               |             | 3.1.4         | Adder and Subtractor Metamutator                            | 47   |

|               | 3.2         | New I         | Designs for Metamutators with Two Active Devices            | 50   |

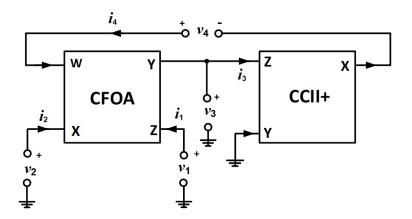

|               |             | 3.2.1         | Realization with One CFOA and One CCII+                     | 51   |

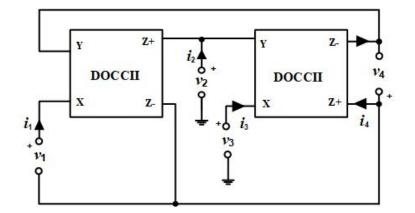

|          |      | 3.2.2   | Realization with Two DOCCII                                | 52  |

|----------|------|---------|------------------------------------------------------------|-----|

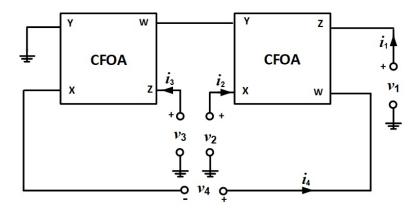

|          |      | 3.2.3   | Realization with Two CFOA                                  | 53  |

|          | 3.3  | New I   | Designs of Metamutators with Single Active Device          | 54  |

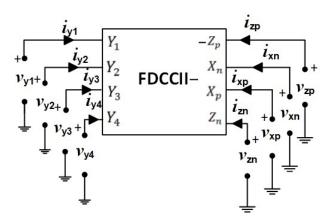

|          |      | 3.3.1   | Realization with Negative Type Fully Differential Current  |     |

|          |      |         | Conveyor (FDCCII-)                                         | 55  |

|          |      | 3.3.2   | Realization with Dual X Current Conveyor (DXCCII)          | 60  |

|          |      | 3.3.3   | Realization with Newly Designed AD-IC                      | 65  |

| 4        | Diff | erent . | Applications of Metamutators                               | 72  |

|          | 4.1  | Realiz  | ation of 1-ports                                           | 73  |

|          |      | 4.1.1   | Mutating Nonlinear Resistor to Memristor                   | 73  |

|          |      | 4.1.2   | Mutating Memristor to Meminductor                          | 75  |

|          |      | 4.1.3   | Mutating Memristor to Memcapacitor                         | 77  |

|          |      | 4.1.4   | Floating and Grounded Impedance Scaling                    | 79  |

|          |      |         | 4.1.4.1 Inductance Simulator                               | 81  |

|          |      |         | 4.1.4.2 Capacitance Multiplier                             | 82  |

|          |      |         | 4.1.4.3 Frequency Dependent Negative Resistor Simulator    | 84  |

|          |      | 4.1.5   | RC-Oscillators                                             | 86  |

|          | 4.2  | Realiz  | ation of 2-Ports                                           | 88  |

|          |      | 4.2.1   | Transconductance Amplifier                                 | 88  |

|          |      | 4.2.2   | Transimpedance Amplifier                                   | 91  |

|          |      | 4.2.3   | Voltage Mode Multiple Input Single Output Universal Filter | 93  |

|          |      | 4.2.4   | Current Mode Single Input Multiple Output Universal        |     |

|          |      |         | Filter                                                     | 98  |

| <b>5</b> | Two  | o Oper  | ationally Nonlinear Applications of AD-IC                  | 103 |

|          | 5.1  | Analo   | g Multiplier                                               | 103 |

|          | 5.2  | Full-V  | Vave Rectifier                                             | 108 |

| 6        | Cor  | nclusio | n                                                          | 113 |

# List of Tables

| 1.1 | Basic circuit elements.                                                                                                         | 1   |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Constitutive relations of all memstors                                                                                          | 5   |

| 1.3 | Mutation table for realizing 1-port elements [4]                                                                                | 16  |

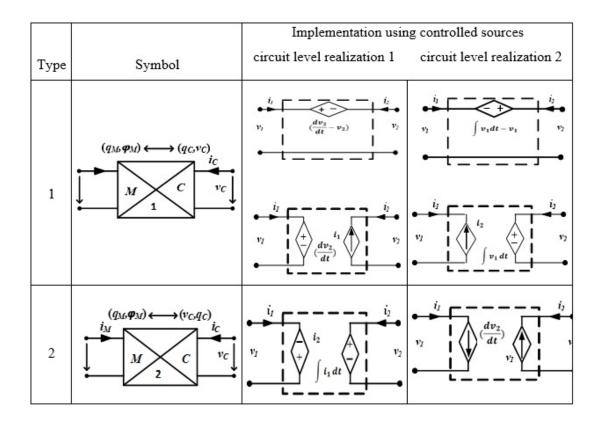

| 2.1 | Different circuit level realizations of M-R mutator                                                                             | 21  |

| 2.2 | Two types and six circuit level realizations of M-L mutators                                                                    | 24  |

| 2.3 | Two types and six circuit level realizations of M-C mutators                                                                    | 26  |

| 2.4 | Two types and four circuit level realizations for ML-MR mutators.                                                               | 28  |

| 2.5 | Two types and four circuit level realizations for MC-MR mutators                                                                | 29  |

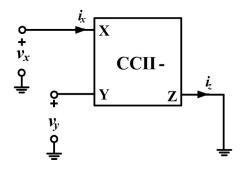

| 3.1 | Dimension of transistors used in CCII+                                                                                          | 35  |

| 3.2 | Dimension of transistors used in CCII                                                                                           | 35  |

| 3.3 | Dimension of transistors used in CF                                                                                             | 40  |

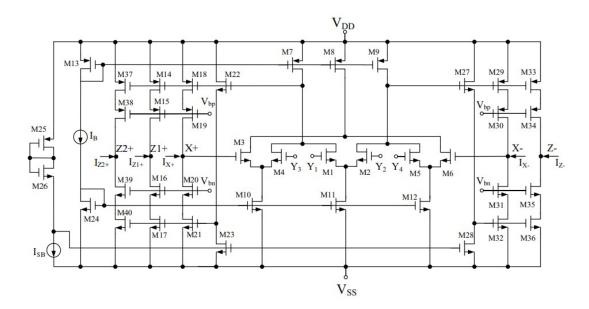

| 3.4 | Dimension of transistors used in FDCCII                                                                                         | 56  |

| 3.5 | Dimension of transistors used in DXCCII                                                                                         | 62  |

| 3.6 | Dimension of transistors used in AD-IC                                                                                          | 65  |

| 3.7 | Comparison between frequency range for optimal operation of<br>incognito metamutators in literature and newly designed of meta- |     |

|     | mutators                                                                                                                        | 70  |

| 3.8 | General comparison between all types of mutators                                                                                | 71  |

| 4.1 | Equivalent impedance at the ports                                                                                               | 80  |

| 4.2 | Different realizations of inductor                                                                                              | 81  |

| 4.3 | Capacitance multiplier realizations                                                                                             | 83  |

| 4.4 | FDNR realizations                                                                                                               | 85  |

| 4.5 | Different 2-port applications and realizations with metamutators .                                                              | 89  |

| 4.6 | Different filter types depending on voltage source locations                                                                    | 95  |

| 4.7 | Transfer functions of different filters                                                                                         | 96  |

| 4.8 | Multifunctional filter realizations                                                                                             | 99  |

| 4.9 | Transfer function of different filters                                                                                          | 100 |

| 5.1 | Transistor dimensions of the squarer circuits                                                                                   | 105 |

| 5.2 | Comparison of the proposed rectifier with others                                                                                | 112 |

# List of Figures

| 1.1  | Basic circuit variables and fundamental 2-terminal elements                       | 2  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | The fourth element memristor completing the symmetry [1]                          | 2  |

| 1.3  | Symbol of memristor and its $\varphi$ -q characteristic                           | 3  |

| 1.4  | Block diagram of metamutator                                                      | 14 |

| 1.5  | (a) Block diagram, (b) Circuit level realization of VIM 4-port                    |    |

|      | metamutator                                                                       | 15 |

| 1.6  | (a) Block diagram, (b) Circuit level realization of CIM 4-port                    |    |

|      | metamutator                                                                       | 15 |

| 2.1  | (a) M-R mutator (b) M-L mutator (c) M-C mutator.                                  | 20 |

| 2.2  | The proposed memristor emulator circuit by L.Chua [1]                             | 22 |

| 2.3  | Implementation of M-R mutator with two CFOAs and one OpAmp                        | 23 |

| 2.4  | Circuit structure of grounded memristor emulator in [110]                         | 23 |

| 2.5  | Lossy memcapacitor emulator and lossy meminductor emulator .                      | 30 |

| 2.6  | MC-MR mutator circuit by Biolek et al                                             | 31 |

| 2.7  | MC-MR mutator circuit by Biolek et al                                             | 31 |

| 2.8  | CCII based meminductor, memcapacitor emulators [11]                               | 32 |

| 2.9  | Meminductor and memcapacitor emulation with dual-output CCII                      | 32 |

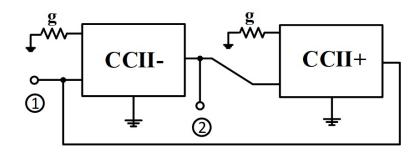

| 3.1  | The gyrator circuit by Sedra and Smith [22]                                       | 34 |

| 3.2  | Diagram of the metamutator obtained from the gyrator circuit in                   |    |

|      | $[22].  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 34 |

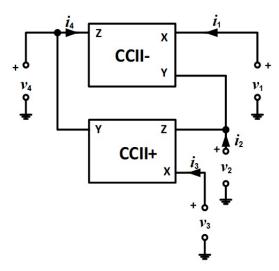

| 3.3  | Block diagram of CCII+                                                            | 34 |

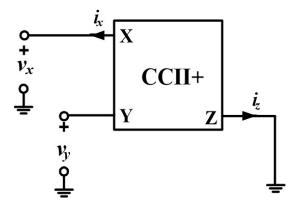

| 3.4  | Block diagram of CCII                                                             | 35 |

| 3.5  | CMOS realization of: (a) (CCII+), (b) (CCII-) $\ldots \ldots \ldots$              | 36 |

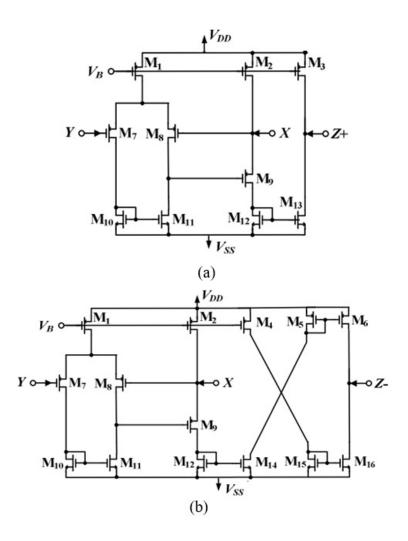

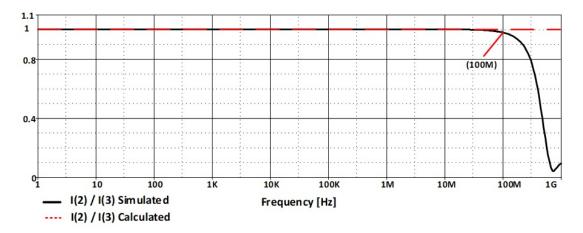

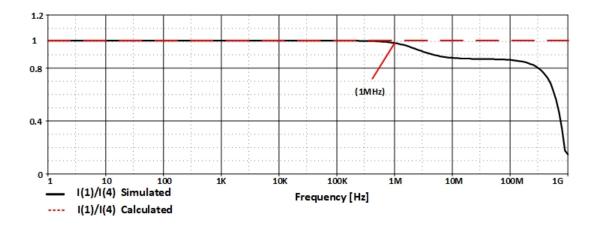

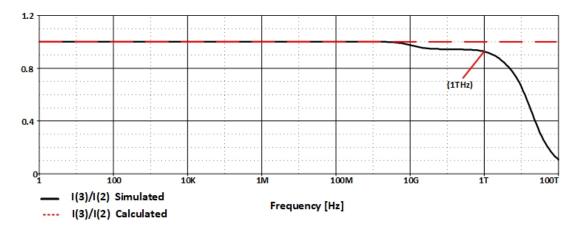

| 3.6  | Theoretical and simulation characteristics of $i_4$ vs. $i_1$                     | 37 |

| 3.7  | Theoretical and simulation characteristics of $i_3$ vs. $i_2$                     | 37 |

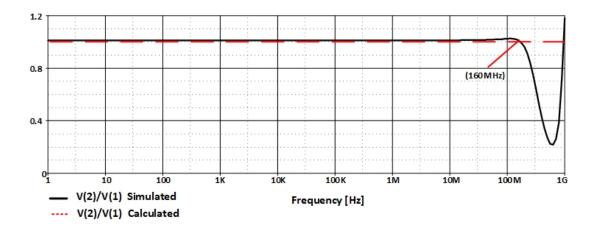

| 3.8  | Theoretical and simulation characteristics of $v_2$ vs. $v_1$                     | 38 |

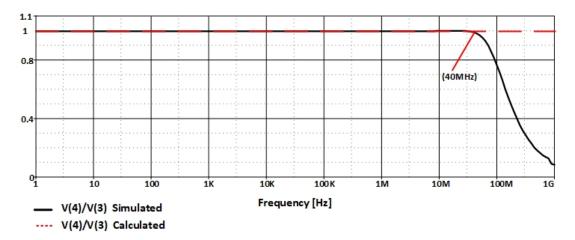

| 3.9  | Theoretical and simulation characteristics of $v_3$ vs. $v_4$                     | 38 |

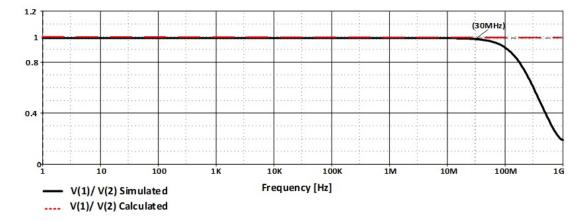

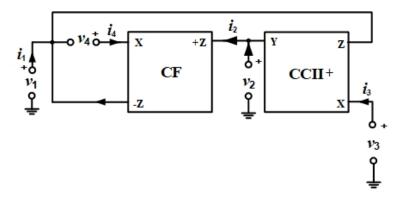

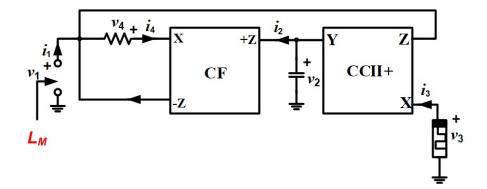

| 3.10 | Metamutator with CCII+ and CF $[27]$                                              | 39 |

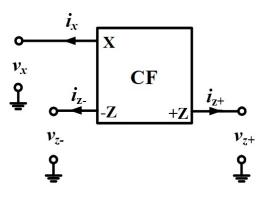

|      | Block diagram of CF                                                               | 39 |

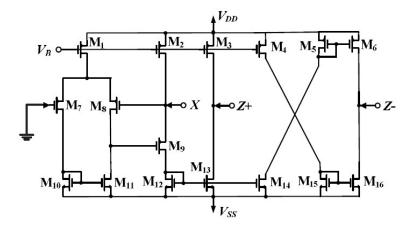

| 3.12 | CMOS realization of CF                                                            | 40 |

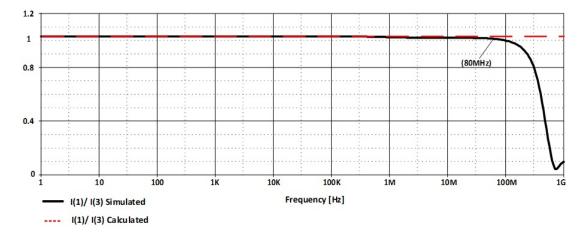

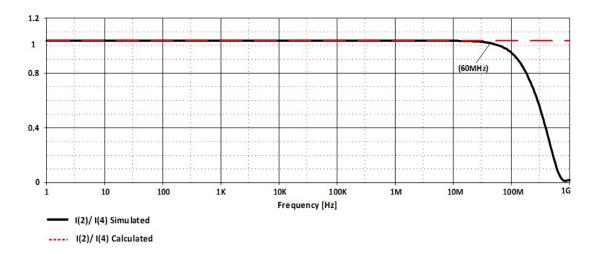

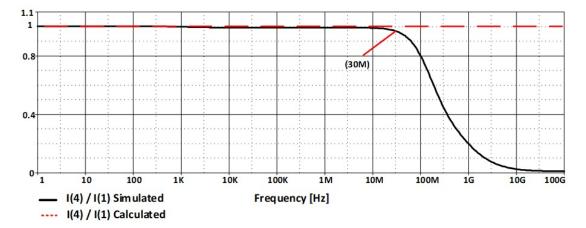

| 3.13 | Theoretical and simulation characteristics of $i_1$ vs. $i_3$                     | 41 |

| 3.14 | Theoretical and simulation characteristics of $i_2$ vs. $i_4$                     | 42 |

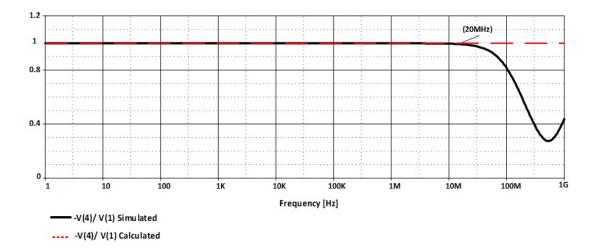

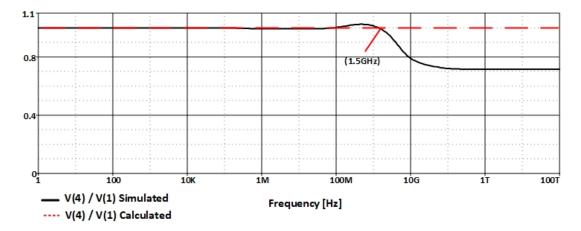

| 3.15 | Theoretical and simulation characteristics of $v_4$ vs. $v_1$                     | 42 |

| 3.16 | Theoretical and simulation characteristics of $v_3$ vs. $v_2$                     | 43 |

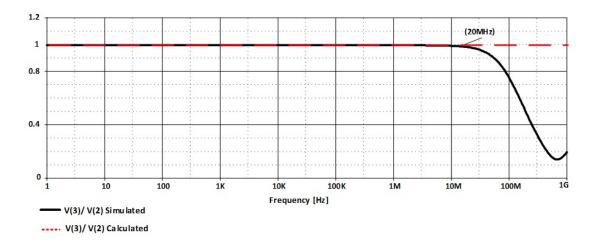

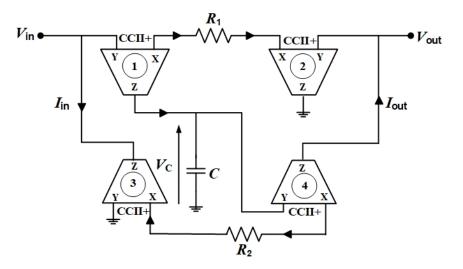

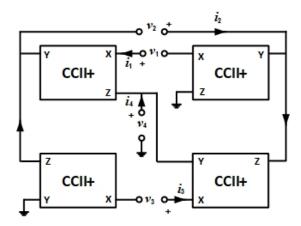

| 3.17 | CCII+ based inductor simulator proposed in [82]                                   | 43 |

|------|-----------------------------------------------------------------------------------|----|

| 3.18 | Diagram of metamutator extracted from [82]                                        | 44 |

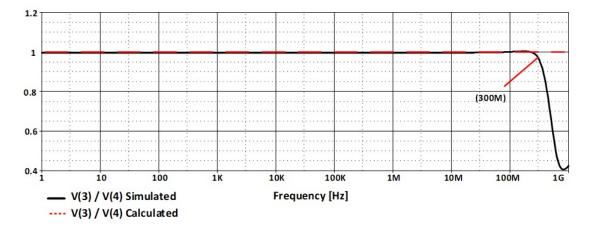

| 3.19 | Theoretical and simulation characteristics of $i_2$ vs. $i_3$                     | 45 |

| 3.20 | Theoretical and simulation characteristics of $i_1$ vs. $i_4$                     | 45 |

| 3.21 | Theoretical and simulation characteristics of $v_3$ vs. $v_4$                     | 46 |

| 3.22 | Theoretical and simulation characteristics of $v_2$ vs. $v_1$                     | 46 |

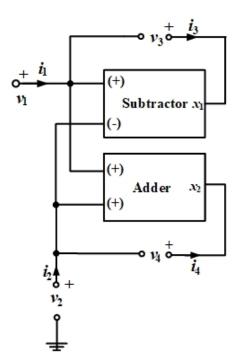

| 3.23 | Generalized 4-port mutator with adder and subtractor $\left[ 24\text{-}26\right]$ | 47 |

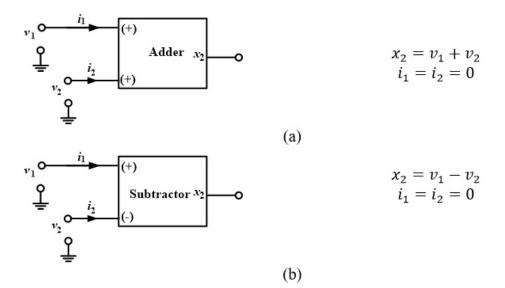

| 3.24 | Block diagrams and defining relations of (a) adder, (b) subtractor.               | 48 |

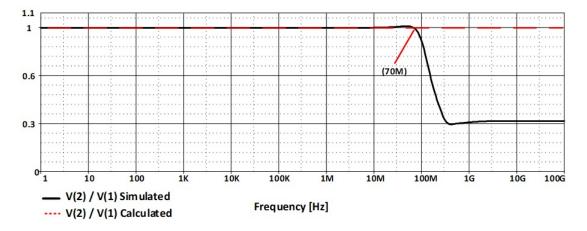

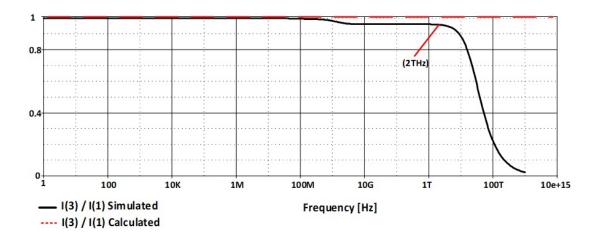

| 3.25 | Theoretical and simulation characteristics of $i_3$ vs. $i_1$                     | 49 |

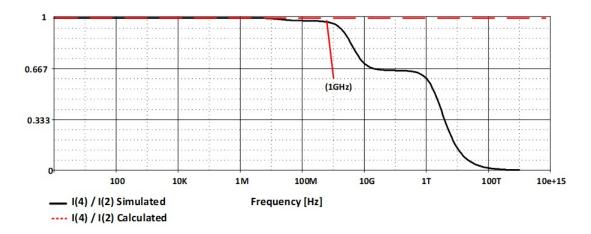

| 3.26 | Theoretical and simulation characteristics of $i_4$ vs. $i_2$                     | 49 |

| 3.27 | Theoretical and simulation characteristics of $v_4$ vs. $v_1$                     | 50 |

| 3.28 | Theoretical and simulation characteristics of $v_3$ vs. $v_2$                     | 50 |

| 3.29 | Metamutator using CFOA and CCII+                                                  | 51 |

| 3.30 | Metamutator with two DOCCIIs                                                      | 52 |

| 3.31 | Metamutator realized with two CFOAs                                               | 53 |

| 3.32 | Block diagram of FDCCII                                                           | 55 |

| 3.33 | CMOS realization of FDCCII- [84]                                                  | 56 |

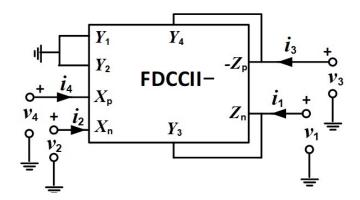

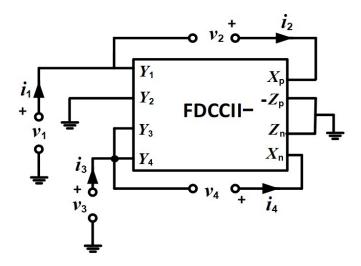

| 3.34 | CIM type metamutator realized with single FDCCII                                  | 57 |

| 3.35 | VIM type metamutator realized with single FDCCII                                  | 58 |

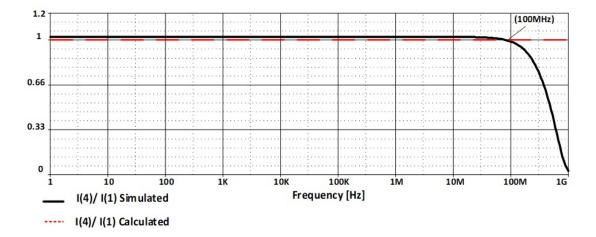

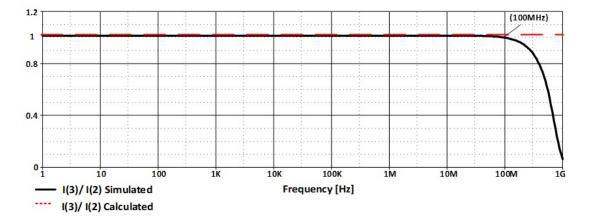

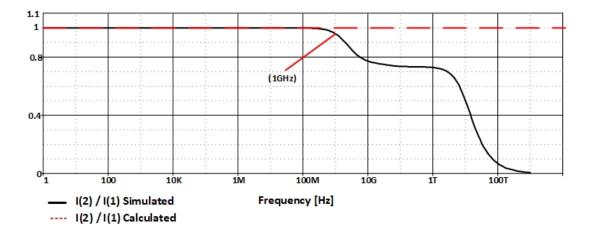

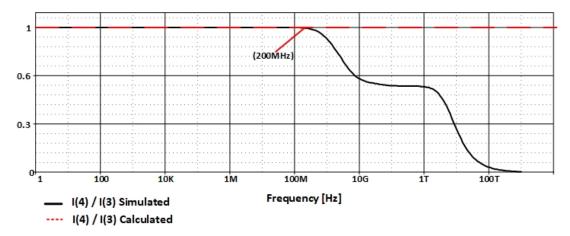

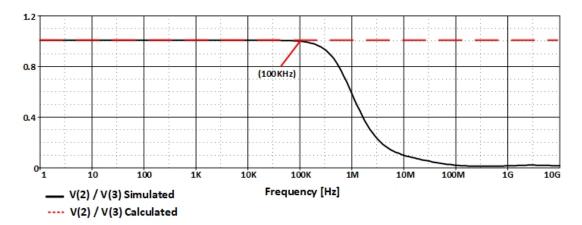

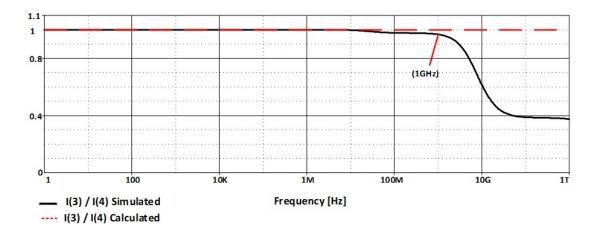

| 3.36 | Ideal and non-ideal gain of $i_1$ and $i_2$                                       | 58 |

| 3.37 | Ideal and non-ideal gain of $i_2$ and $i_3$                                       | 59 |

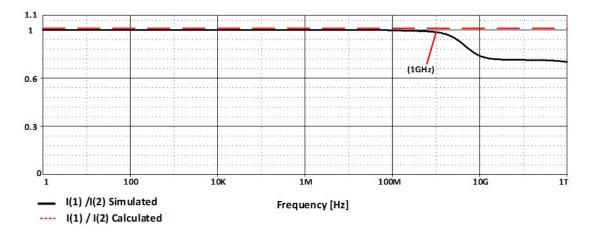

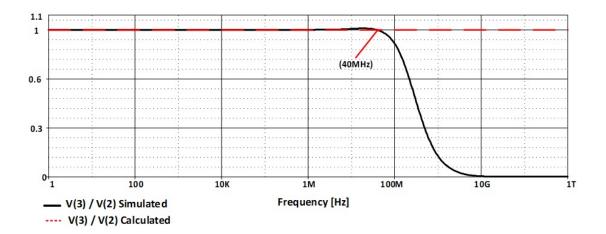

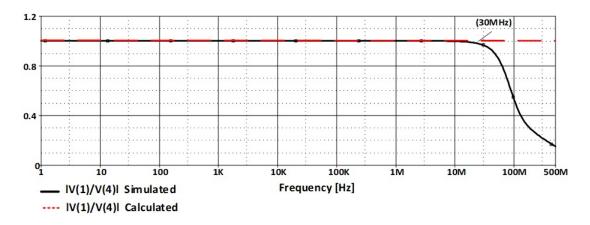

| 3.38 | Ideal and non-ideal gain of $v_2$ and $v_3$                                       | 59 |

| 3.39 | Ideal and non-ideal gain of $v_4$ and $v_1$                                       | 60 |

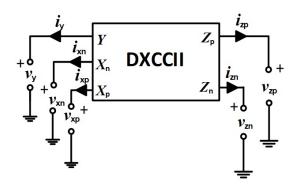

| 3.40 | Schematic block diagram of DXCCII                                                 | 61 |

| 3.41 | CMOS realization of DXCCII                                                        | 61 |

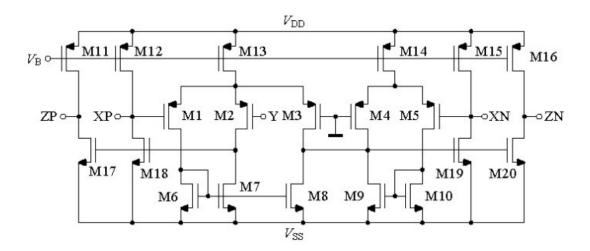

| 3.42 | Newly proposed metamutator with DXCCII                                            | 62 |

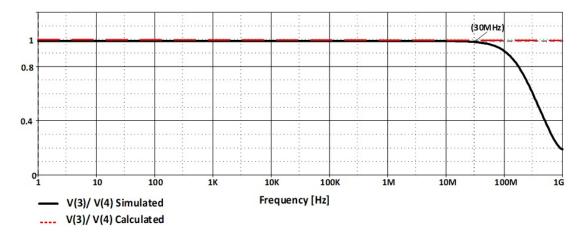

| 3.43 | Ideal and non-ideal gain of $i_1$ and $i_4$                                       | 63 |

| 3.44 | Ideal and non-ideal gain of $i_3$ and $i_2$                                       | 63 |

| 3.45 | Ideal and non-ideal gain of $v_2$ and $v_1$                                       | 64 |

| 3.46 | Ideal and non-ideal gain of $v_4$ and $v_3$                                       | 64 |

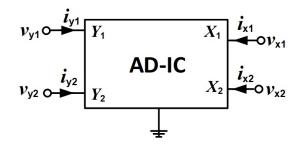

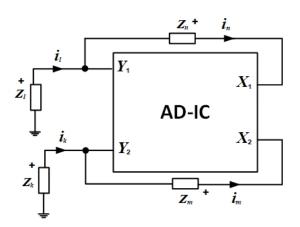

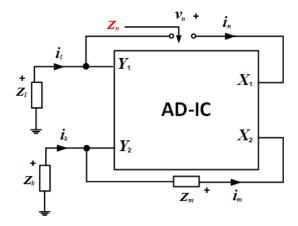

| 3.47 | Schematic block diagram of AD-IC                                                  | 65 |

| 3.48 | The implementation of AD-IC with twelve MOS transistors                           | 66 |

| 3.49 | Layout of the AD-IC circuit                                                       | 66 |

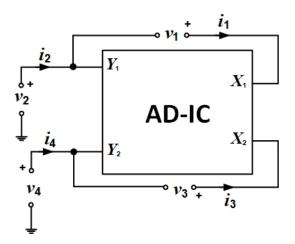

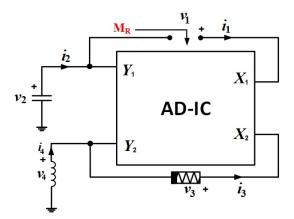

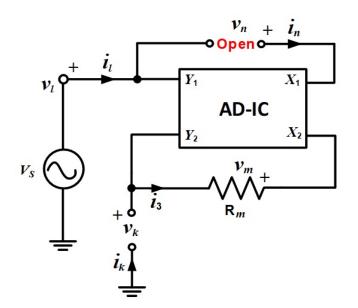

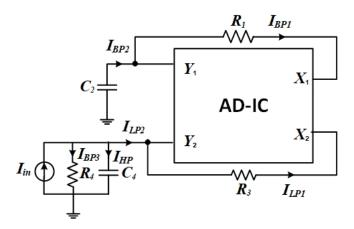

| 3.50 | Schematic diagram of metamutator with AD-IC                                       | 67 |

| 3.51 | Ideal and non-ideal gain of $i_3$ and $i_4$                                       | 68 |

| 3.52 | Ideal and non-ideal gain of $i_1$ and $i_2$                                       | 68 |

| 3.53 | Ideal and non-ideal gain of $v_3$ and $v_2$                                       | 69 |

| 3.54 | Ideal and non-ideal gain of $v_4$ and $v_1$                                       | 69 |

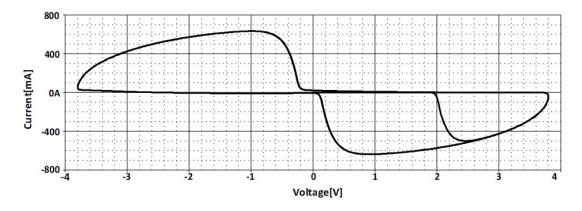

| 4.1  | Memristor realization with AD-IC based metamutator                                | 73 |

| 4.2  | Implementation on non-linear load of M-R mutators.                                | 73 |

| 4.3  | i-v characteristic of memristor                                                   | 75 |

| 4.4  | Meminductor realization with memristor terminated metamutator                     | 75 |

| -• - |                                                                                   | .0 |

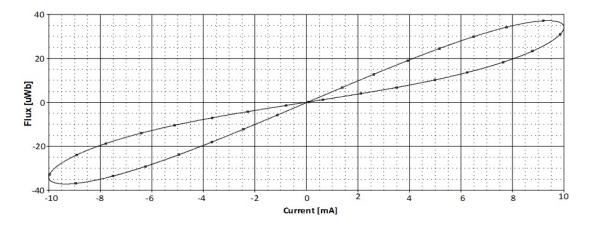

| 4.5  | $\varphi - i$ characteristic of meminductor $\ldots \ldots \ldots \ldots \ldots \ldots$ | 77  |

|------|-----------------------------------------------------------------------------------------|-----|

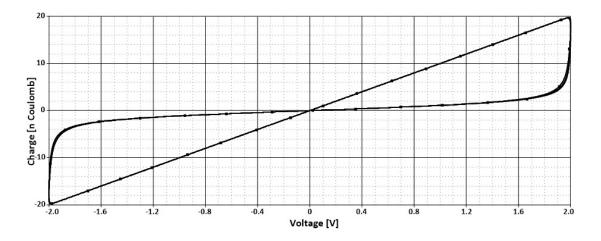

| 4.6  | Memcapacitor realization with memristor terminated metamutator                          | 78  |

| 4.7  | $q-v$ characteristic of the memcapacitor $\ldots \ldots \ldots \ldots \ldots \ldots$    | 79  |

| 4.8  | Metamutator terminated with port impedances                                             | 79  |

| 4.9  | Port $n$ of metamutator terminated with impedance $Z_n$                                 | 80  |

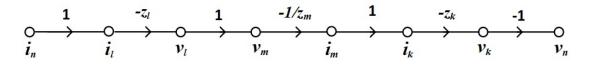

| 4.10 | Impedance scaling calculated with signal flow-graph                                     | 80  |

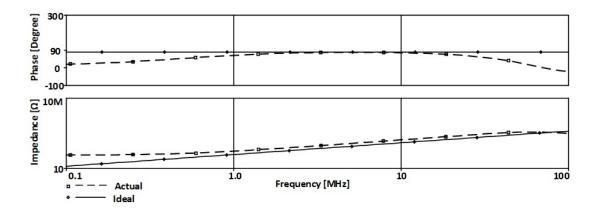

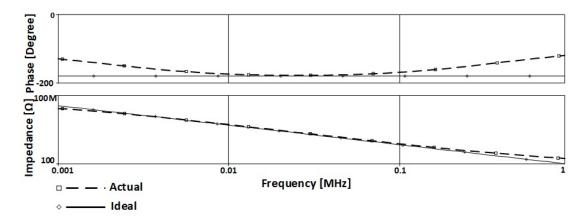

| 4.11 | Phase and  impedance  plots of the inductor vs. frequency                               | 82  |

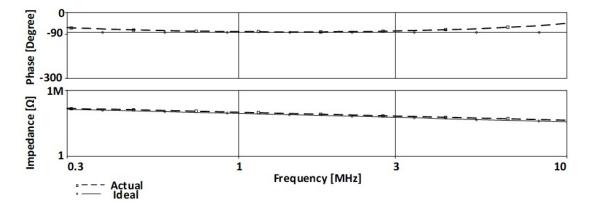

| 4.12 | Phase and  impedance  plots of the capacitor vs. frequency                              | 83  |

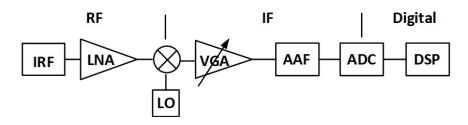

| 4.13 | Schematic of fully digital receiver [31]                                                | 84  |

| 4.14 | Characteristics of FDNR in frequency domain                                             | 85  |

| 4.15 | Block diagram of the RC-oscillator                                                      | 86  |

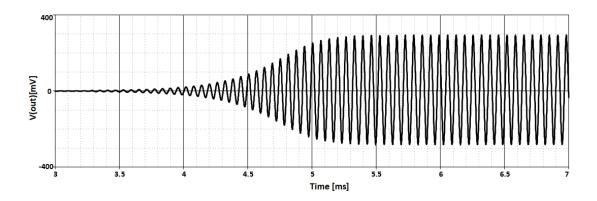

| 4.16 | Simulation result of RC-oscillator                                                      | 88  |

| 4.17 | Transconductance amplifier realization $#4$                                             | 90  |

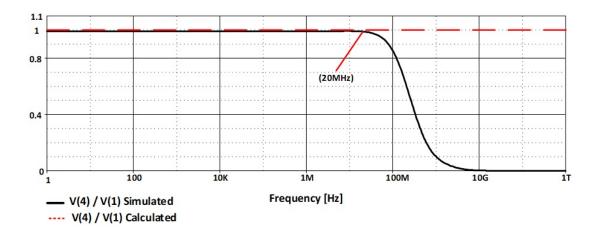

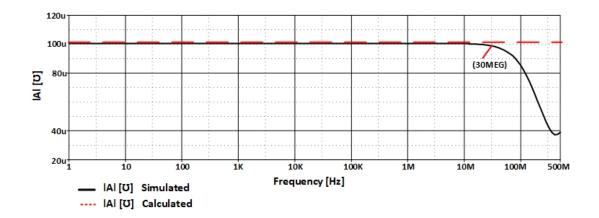

|      | $\rm I/O$ characteristics vs. frequency of transconductance amplifier                   | 91  |

| 4.19 | Circuit of transimpedance amplifier realization $#2$ of Transimpedan                    |     |

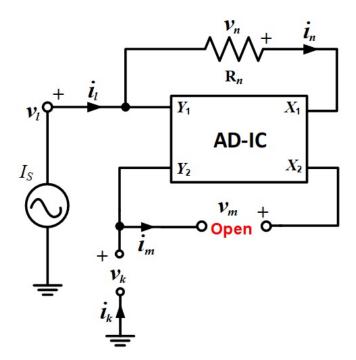

|      | Amplifier                                                                               | 92  |

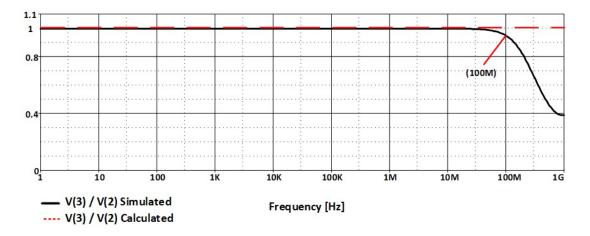

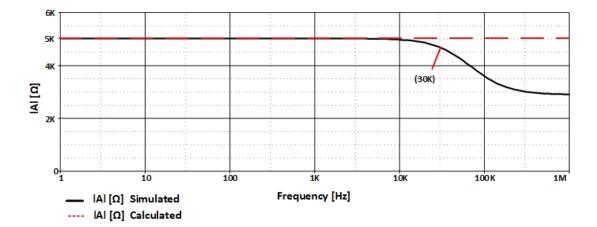

|      | $\rm I/O$ characteristics vs frequency of transimpedance amplifier $~.~.~$              | 92  |

|      | Universal filter structure                                                              | 94  |

|      | VIM based VM-MISO universal filter                                                      | 95  |

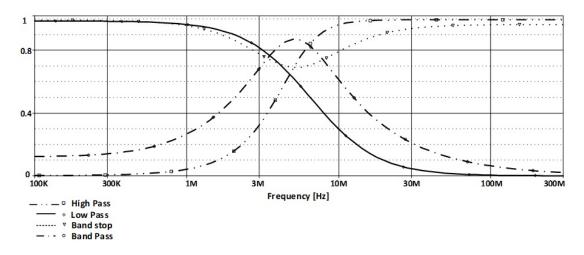

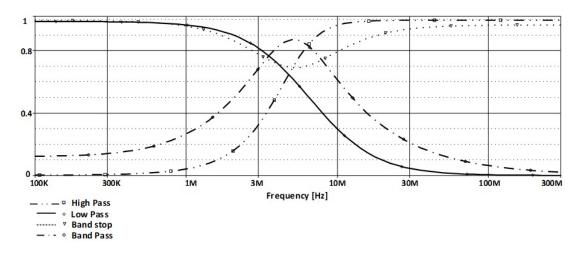

|      | Simulation results of all filter types                                                  | 96  |

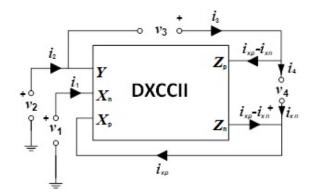

|      | Circuit diagram of the CM-SIMO universal filter                                         | 99  |

|      | Current mode filter realization $#4$                                                    | 100 |

| 4.26 | Simulation results of all type filters                                                  | 101 |

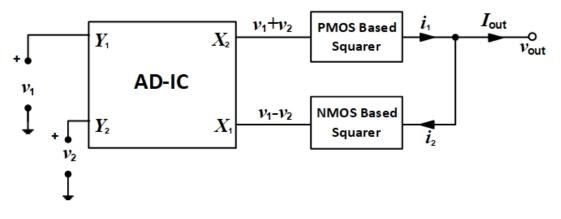

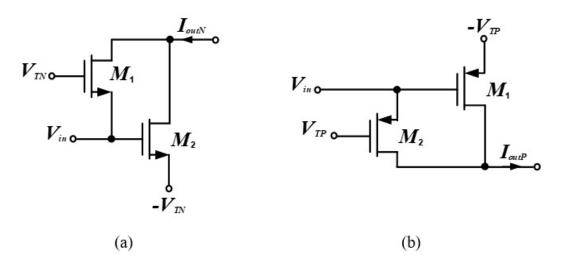

| 5.1  | Block diagram of proposed multiplier                                                    | 104 |

| 5.2  | Voltage in/current out squarer circuits: (a) NMOS-based, (b)                            |     |

|      | PMOS-based                                                                              | 105 |

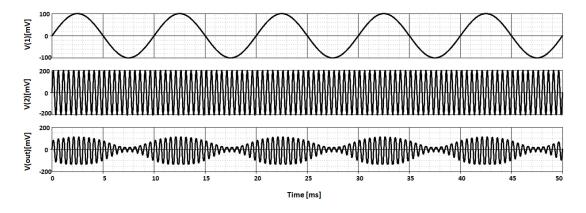

| 5.3  | Simulation result of multiplier as modulator                                            | 107 |

| 5.4  | Block diagram of AD-IC                                                                  | 109 |

| 5.5  | Time-domain input and output waveforms of the rectifier with                            |     |

|      | AD-IC                                                                                   | 111 |

| 5.6  | DC characteristics of the non-inverting full-wave rectifier circuit .                   | 111 |

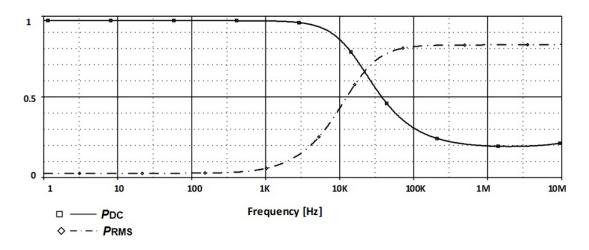

| 5.7  | $P_{DC}, P_{(RMS)}$ characteristics of the rectifier in 100mV input ampli-              | 110 |

|      | tude                                                                                    | 112 |

# List of Abbreviations

| $\mathbf{AC}$          | Alternative Current                                                                                                                           |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                    | Analog to Digital Converter                                                                                                                   |

| AD-IC                  | $\mathbf{A}$ dditive- and $\mathbf{D}$ ifferentiative Integrated Circuit                                                                      |

| AM                     | $\mathbf{A} m plitude \ \mathbf{M} odulator$                                                                                                  |

| Ap                     | All Pass                                                                                                                                      |

| BP                     | Band Pass                                                                                                                                     |

| CCCDBA                 | Current Controlled Current Differencing BufferedAmplifiers                                                                                    |

| CCCII                  | Current Controlled Current Conveyor                                                                                                           |

| CCII+                  | Plus Type II. generation Current Conveyor                                                                                                     |

| CCII-                  | Minus Type II. generation Current Conveyor                                                                                                    |

| $\mathbf{CF}$          | $\mathbf{C}$ urrent $\mathbf{F}$ ollower                                                                                                      |

| CFOA                   | Current <b>F</b> eedback <b>O</b> perational <b>A</b> mplifier                                                                                |

| CIM                    | $\mathbf{C}$ urrent $\mathbf{I}$ nverting $\mathbf{M}$ etamutator                                                                             |

| $\mathbf{C}\mathbf{M}$ | $\mathbf{C}$ urrent $\mathbf{M}$ ode                                                                                                          |

| CMOS                   | Complementary Metal Oxide Semiconductor                                                                                                       |

| DC                     | Direct Current                                                                                                                                |

| DOCCII                 | Dual Output Current Conveyor                                                                                                                  |

| DO-OTA                 | $\mathbf{D} \text{ual } \mathbf{O} \text{utput } \mathbf{O} \text{perational } \mathbf{T} \text{ransconductance } \mathbf{A} \text{mplifier}$ |

| DSBSC                  | Double Sideband Suppressed Carrier Alternative Current                                                                                        |

| DVCC                   | Differential Voltage Current Conveyor                                                                                                         |

| DXCCII                 | DualX Current Conveyor                                                                                                                        |

| FDCCII                 | Fully Differential Current Conveyor                                                                                                           |

| FDNR                   | Frequency Dependent Negative Resistor                                                                                                         |

| HP                     | $\mathbf{H}\text{ewllet}\;\mathbf{P}\text{ackard}$                                                                                            |

| HP                     | $\mathbf{H} \mathrm{igh} \; \mathbf{P} \mathrm{ass}$                                                  |

|------------------------|-------------------------------------------------------------------------------------------------------|

| JFET                   | Junction Field Effect Transistor                                                                      |

| KCL                    | Kirchoff's Current Law                                                                                |

| KVL                    | Kirchoff's Voltage Law                                                                                |

| LP                     | Low Pass                                                                                              |

| $\mathbf{MC}$          | $\mathbf{Mem}\mathbf{C}$ apacitor                                                                     |

| $\mathbf{ML}$          | $\mathbf{M}\mathbf{em}\mathbf{Inductor}$                                                              |

| $\mathbf{MR}$          | $\mathbf{Mem}\mathbf{R}$ istor                                                                        |

| NMOS                   | Negative Metal Oxide Semiconductor                                                                    |

| OPAMP                  | $\mathbf{OP}$ erational $\mathbf{AMP}$ lifier                                                         |

| OTA                    | $\mathbf{O} \mathrm{perational} \ \mathbf{T} \mathrm{ransconductance} \ \mathbf{A} \mathrm{mplifier}$ |

| PMOS                   | $\mathbf{P} ositive \ \mathbf{M} etal \ \mathbf{O} xide \ \mathbf{S} emiconductor$                    |

| TSMC                   | ${\bf T}aiwan \; {\bf S} emiconductor \; {\bf M} anufacturing \; {\bf C} or poration$                 |

| VIM                    | Voltage Inverting Metamutator                                                                         |

| $\mathbf{V}\mathbf{M}$ | $\mathbf{V} oltage \ \mathbf{M} ode$                                                                  |

#### Chapter 1

### Introduction

#### 1.1 Basic Circuit Elements and Memstors

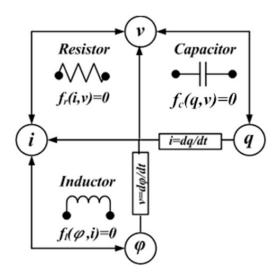

As it is well known there are four basic circuit variables: electrical charge q, current i (being the derivative of charge), voltage v and flux  $\varphi$  (being the derivative of flux); also only three fundamental, two-terminal circuit elements were known and used: resistor, capacitor and inductor. The behavior of these circuit elements is described by an algebraic relationship between two of the four basic circuit variables.

| $f_R(i,v) = 0$        | Resistor  |

|-----------------------|-----------|

| $f_C(q,v) = 0$        | Capacitor |

| $f_L(\varphi, i) = 0$ | Inductor  |

TABLE 1.1: Basic circuit elements.

According to Table 1.1 a symbolic graph can be visualized that depicts the constitutive (defining) relations between current-voltage, charge-voltage and fluxcurrent respectively as shown in Figure 1.1. It is the missing link between flux  $\varphi$ and electrical charge q that led to the discovery of memristor.

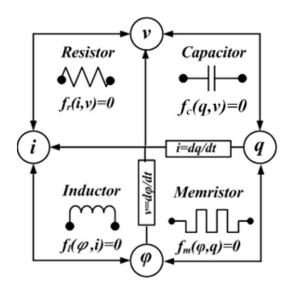

In 1971, Leon Chua completed the symmetry by introducing the relation between  $\varphi$  and q and, calling the resulting element a memristor an acronym obtained by combining MEMory and ResISTOR. Thus a memristor is a 2-terminal circuit element with an algebraic constitutive relation between its charge and flux [1].

Figure 1.1: Basic circuit variables and fundamental 2-terminal elements

Figure 1.2: The fourth element memristor completing the symmetry [1]

The general expression of a time-invariant memristor is:

$$f_M(\varphi, q) = 0 \tag{1.1}$$

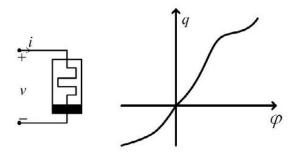

The symbol and a hypothetical  $\varphi$ -q curve of the memristor are shown in Figure 1.3.

Figure 1.3: Symbol of memristor and its  $\varphi$ -q characteristic

Based on dependency between charge and flux of memristor there are two types of memristors: charge controlled and flux controlled memristors.

If  $\varphi$  is a function of q the memristor is *charge controlled*, if q is a function of  $\varphi$  the memristor is *flux controlled*. For a charge controlled memristor:

$$\varphi = f(q) \tag{1.2}$$

Assuming that f in (1.2) is differentiable, by taking time derivative of both sides of (1.2) and applying the chain rule the *v*-*i* dependence for a memristor becomes:

$$v(t) = \frac{d\varphi(t)}{dt} = \frac{df(q)}{dq} \cdot \frac{dq}{dt} = M(q(t)) \cdot i(t)$$

(1.3)

Thus,

$$v(t) = M(q(t)).i(t)$$

(1.4)

where M(q(t)) = df(q)/dq is the Memristance with Ohm ( $\Omega$ ) as unit, justifying the inclusion of "ristor" into the name.

In a *flux controlled* memristor the charge q is a function of  $\varphi$ ,

$$q = f(\varphi) \tag{1.5}$$

Again by taking time derivative of both sides of (1.5) and applying the chain rule, (1.6) becomes:

$$i(t) = \frac{dq(t)}{dt} = \frac{df(\varphi)}{d\varphi} \cdot \frac{d\varphi}{dt} = W(\varphi(t)) \cdot v(t)$$

(1.6)

Thus,

$$i(t) = W(\varphi(t)).v(t) \tag{1.7}$$

where  $W(q(t)) = df(\varphi)/d\varphi$  is Memductance and has the unit of Siemens ( $\mho$ ). Comparing (1.4) and (1.7), one obtains:

$$M(q(t)) = \frac{1}{W(\varphi(t))} \tag{1.8}$$

Again from (1.4) and (1.7) it is easily observed that when the current through the memristor is zero its voltage is also zero, and vice versa thus forcing the characteristic to go through the origin. Thus by applying a sinusoidal current or voltage signal to the memristor its current-voltage characteristic becomes a Lissajous curve also passing through the origin.

In 1976, Chua and Kang in [2] introduced memristive systems by extending the concept of memristor to a class of nonlinear dynamical systems and in 2010 Ventra et al. extended the notion of memristive systems to capacitive and inductive elements with properties depending on the state and history of the system just like memristor [3]. By applying sinusoidal inputs all these elements show pinched hysteretic loops between two constitutive variables that define them: *current-voltage* for memristor, *charge-voltage* for memcapacitor, and *current-flux* for meminductor.

Finally, it should be observed that for a linear memristor M(q) and  $W(\varphi)$  reduce to constants hence to simple linear resistors, explaining why memristor was discovered so late.

Memstor, a term introduced in [4], is a generic name for the class of 2-terminal elements with memory such as memristor, meminductor, memcapacitor, which are devices whose terminal behavior depends nonlinearly on the initial state and the history of the applied input to the system. All memstors are summarized in Table 1.2 where  $\sigma$  is the time integral of charge and  $\rho$  is the time integral of flux.

| Charge-controlled memristor    |                                                                                   |

|--------------------------------|-----------------------------------------------------------------------------------|

|                                | $v(t) = M\left(q_0 + \int_0^t i(\tau)d\tau\right)i(t)$                            |

| Flux-controlled memristor      |                                                                                   |

|                                | $i(t) = W\left(\varphi_0 + \int_0^t v(\tau)d\tau\right)v(t)$                      |

| Charge-controlled memcapacitor |                                                                                   |

|                                | $v(t) = D_M \left(\sigma_0 + \int_0^t q(\tau) d\tau\right) q(t)$                  |

| Flux-controlled memcapacitor   |                                                                                   |

|                                | $q(t) = C_M \left(\varphi_0 + \int_0^t v(\tau) d\tau\right) v(t)$                 |

| Charge-controlled meminductor  |                                                                                   |

|                                | $\varphi(t) = L_M \left( q_0 + \int_0^t i(\tau) d\tau \right) i(t)$               |

| Flux-controlled meminductor    |                                                                                   |

|                                | $i(t) = \Gamma_M \left( \rho_0 + \int_0^t \varphi(\tau) d\tau \right) \varphi(t)$ |

TABLE 1.2: Constitutive relations of all memstors

#### 1.2 Literature Review

In 1968 Leon Chua in [5] claimed that it is possible to mutate one type of circuit element, be it linear or nonlinear, into another by using a 2-port mutator and he first proposed three types of mutators for this purpose. Then in 1971, after introducing "memristor" as the fourth circuit element, he presented the first M-R mutator circuit with a highly complex structure for the purpose of realizing memristors from nonlinear resistors [1].

Due to the invaluable properties of memristor such as non-volatile memory element and/or its nonlinear characteristics, this element has been used in various applications like the design of analog and digital circuits, neuromorphic circuits, chaotic systems etc. [6], [84], [85], [86], [87].

Hewlett Packard (HP) research team in 2008 successfully realized the first memristor as a simple 2-terminal device using thin film Titanium dioxide (TiO2), which can be viewed as a 2-terminal resistor with changing resistance depending on the voltage or current applied to it [83]. Despite this successful realization, memristors are not yet commercially available and their modeling is essential to memristor based circuit and system design. Thus researchers have been encouraged to develop simple SPICE macro models [120-124].

Another approach is the use of mutator circuits, constructed using off-the-shelf devices which are commercially available in the market [98-102], [104-105], [107], [109-112] to mutate the dynamic behavior of conventional elements to that of a memristor hence the need and emphasis on "Mutators". Mutators not only convert one type of element to another in simulations they also make hard realizations of unavailable 2-terminal elements possible and thus provide means to experiment in the lab with them.

A literature survey shows a very large number of mutator realizations, possessing weaknesses such as:

- i. The use of an excessive number of active elements,

- ii. Excessive use of grounded and/or floating passive elements,

- iii. Usage of ungrounded capacitors; using grounded capacitors in integrated circuit (IC) implementation has considerable advantages [116],

- iv. Use of analog multiplier for the purpose of obtaining nonlinearity property of memristor, causes to increasing the number of used active elements, which resulting in higher power consumption also large chip area occupation.

For instance, the memristor emulator presented in [113] uses a Microcontroller, an Analog to Digital Converter (ADC) and a Digital to Analog Converter (DAC) blocks and one low pass filter. This emulator is topologically complex which limits its applicability due to difficulty in interconnecting with active and passive devices. The proposed emulator circuit suffers from weakness i.

An Electronically Tunable Differential Different Current Conveyor (EDDCC) and a multiplier are used to implement the memristor emulator circuit proposed in [114]. Six OTAs are employed in the structure of EDDCC. However, the experimental results using this mutator circuit do not satisfy the properties of a memristor and the hysteresis loop area does not decrease as frequency increases. Also, the proposed emulator circuit suffers from weaknesses i and iv.

A CMOS based memristor emulator has been introduced in [115]. Single CCII+, one grounded capacitor and one Voltage Controlled Resistor (VCR) are employed in the implementation of the emulator. Also, two OPAMPs, a single transistor, two floating capacitors and six resistors are utilized in VCR implementation. Due to complexity of the structure and use of floating capacitors this emulator configuration is not suitable for real world hardware applications. Briefly the proposed emulator circuit suffers from disadvantages i, ii and iii.

In [98] a floating memristor with four OPAMPs, single analog multiplier, ten transistors, single capacitor and eight resistors in its structure was presented. Both simulation and experimental results are given in the paper. There are three important properties to be considered in a memristor emulator: memory effect, frequency dependent characteristic, and nonlinearity. Memory effect and frequency dependency characteristic are obtained by using a capacitor. Nonlinearity is implemented using multiplier circuit. But each used block gives rise to extra power dissipation and more complex circuit also, simulations have not been performed at transistor level. Briefly proposed mutator circuit suffers from i, iii and iv.

Yesil et al. proposed a floating memristor emulator employing a single Differential Difference Current Conveyor (DDCC), one analog multiplier and two resistors, one floating and one grounded capacitor [99]. The capacitor provides the memory effect and the multiplication of capacitor and resistor voltages is connected to the Y terminal of the active device. However, the memristor can be operated only at high frequencies such as in the order of MHz which contradicts the essential properties of memristor also, the proposed mutator circuit suffers from weakness i.

In [100] a floating memristor emulator including four CFOAs, one multiplier and six passive elements in its structure have been proposed. Both simulation and experimental results are given in the paper. However, the simulations are not done at transistor level and the proposed memristor mutator circuit suffers from i, ii, iv.

In [101] a floating memristor emulator containing four CFOAs, single analog multiplier, single OPAMP and nine passive elements, where some of the elements are floating is presented. The memristance value of obtained memristor is not electronically tunable. The emulator circuit is complex, bulky, suffering from i, ii, iv.

In [104], a grounded memristor emulator made of two CFOAs, a single analog multiplier and seven grounded/floating passive elements has been proposed. The

optimal frequency range of the obtained memristor is 16Hz - 160kHz. Both simulation and experimental results of the presented memristor emulator have been given to confirm its feasibility and workableness. However, the simulations are not at transistor level and commercially available active devices have been used instead of CFOAs and analog multiplier. The proposed memristor mutator circuit suffers from weakness i, ii and iv.

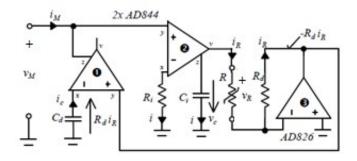

A CCII based charge controlled memristor emulator containing single CCII, single analog multiplier, single floating resistor and a grounded capacitor was presented in [105]. However, the memristance value of obtained memristor is not electronically tunable. Also, commercially available active devices AD633 and AD844 have been utilized instead of multiplier and CCII+, respectively. Briefly the proposed emulator circuit suffers from disadvantages i, ii and iv.

A tunable floating memristor emulator circuit consisting of single multiple-output OTA (MO-OTA), single analog multiplier and two grounded passive elements was proposed in [106]. This emulator derived from the one in [99] has the advantage of its memristance value being adjustable by biasing the current of the OTA. The proposed emulator, despite its simplicity in design, suffers from iv.

One grounded voltage controlled and one grounded current controlled memristor emulators were reported in [107]. In the structure of current-controlled memristor emulator, two CCII+s, a single analog multiplier, a single buffer as active devices and three grounded one floating passive components are being used, while the voltage controlled memristor emulator consists of three CCII+s, a single analog multiplier, single buffer and six grounded passive elements. The circuit structures of both mutators are highly complex and suffer from weakness i, ii and iv. Also, the memristance values of obtained memristors are not electronically tunable.

Using single Current Backward Transconductance Amplifier (CBTA), single analog multiplier, two resistors and one grounded capacitor, a grounded memristor emulator is proposed in [108]. In this emulator Memory effect and frequency dependency properties of memristor are implemented by using a capacitor and the nonlinearity property is obtained by using multiplier. The proposed emulator suffers from iv.

In [3] Pershin and Ventra, using off-the-shelf components like one microcontroller, one Analog to Digital Converter (ADC) and one digital potentiometer with its resistance defined by a digital code written in it, built a rather complex and expensive floating memristor emulator. The proposed memristor emulator suffers from i and ii.

In [102], a new floating memristor emulator consisting of three OTAs, four CCIIs, and seven passive elements, three of them floating, has been presented. Both simulation and experimental results of the presented memristor emulator have been given to confirm its feasibility and workability. Commercially available active devices CA3080 and AD844 have been used instead of OTA and CCII in simulations and experiments. However, the circuit configuration is complex and bulky and suffers from weaknesses i and ii.

In [103] a floating memristor emulator has been presented. The circuit of the emulator consists of one OTA, one multiplier, two MOS transistor and two grounded capacitors. The memristance value cannot be tuned electronically. The proposed emulator circuit suffers from iv.

A grounded memristor emulator employing ten DDCC active elements, eight transistors and five passive elements has been presented in [109]. However, the proposed emulator circuit suffers from i and ii. Each active device giving rise to extra power dissipation and a more complex circuit.

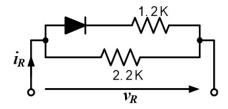

A generalized mutator for the purpose of realizing inductors, memristors, meminductors and memcapacitor has been reported in [4]. The memristor can be obtained by employing single adder, single subtractor, grounded diode, floating inductor and capacitor, without using an analog multiplier. The diode provides the non-linear resistor in the circuit. This circuit is able to convert all types of circuit elements to each other and the idea of metamutator was first introduced in this article.

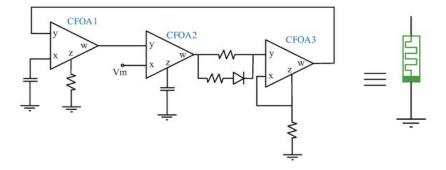

Two grounded memristor emulator configurations were presented in [110]. Each circuit comprises three CFOAs, four resistors, two capacitors, and one diode without using an analog multiplier. Nonlinear characteristic is provided by a diode. CFOA which is an active element, is modeled by AD844, a commercially available active device, and experimental results have been provided. Likewise, in [111], comprising of two CFOAs, a single OTA and five grounded passive elements a grounded memristor emulator again without using an analog multiplier is introduced. The proposed emulator circuits suffer from i and ii.

In [112] a grounded memristor emulator including Single Differential Voltage Current Conveyor Transconductance Amplifier (DVCCTA), one grounded capacitor, three resistors, one of them floating, is presented. Both simulation and experimental results of the memristor emulator are given in the paper. As for experiments a single CA3080, four AD844s and nine passive elements provided the implementation of DVCCTA. Due to its highly complex structure this emulator is not suitable for IC designs. The proposed emulator circuit suffers from i and ii.

In [119] a memristor emulator based on a light dependent resistor (LDR), with its resistance easily reconfigurable by a controlling voltage, is introduced. However, the memristance value of the memristor, realized due to the nonlinearity of the LDR, is hard to calculate accurately. Also the complexity and difficulty of practical implementation of the introduced emulator are the other disadvantages. The proposed emulator circuit suffers from i. ii and iii.

Memcapacitive and meminductive systems are two classes of circuit elements with memory that complete memstors ie. the class of memristive systems [1,2]. When driven by a periodic input, their characteristics are hysteretic loops between their constitutive variables current–flux for meminductors and voltage–charge for memcapacitors which pass through the origin [118]. Meminductor and memcapacitor are able to store energy and this significant ability distinguishes these elements from memristor. Due to lack of availability of meminductor and memcapacitor as off the shelf components, just like the memristor, there are many different emulator circuits in literature for simulating meminductor and memcapacitor with active and passive components together.

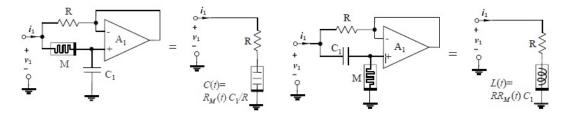

In 2010 Pershin and Ventra, by using one OpAmp and several passive components, introduced mutator circuits for realizing lossy meminductors and lossy memcapacitors from memristors [7]. In simulations they have used the memristor emulator circuit in [3] and shown an interesting connection between three memory elements. The proposed emulator circuit suffers from iii.

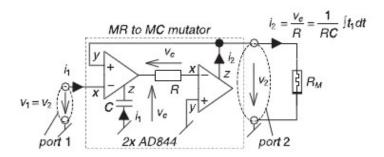

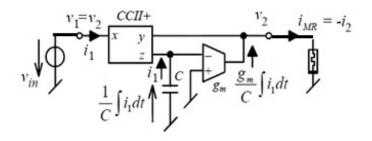

In [8] a mutator circuit for mutating memristor to memcapacitor by employing inexpensive off-the-shelf components like, two OTAs and several passive components was reported. The presented mutator provides a true memristor into memcapacitor mutation. However, the proposed mutator is able to mutate only memcapacitor from memristor Also, simulations are not in transistor levels and for OTAs AD844 commercial device is used. In [9] mutator circuit for mutating memristor to memcapacitor is presented. The main idea of circuit design is the same as [8] and instead of two OTAs one CCII+ and one OTA is used in the structure of mutator circuit. In simulations the constitutive relation of the memristor is preserved, within scaling, by the elements obtained after the mutation Also simulation results confirm an important fingerprint of mem-elements, namely the gradually decreasing hysteretic effects with increasing input frequency. However, gain simulations have not been done at transistor level and AD844 commercial device is used instead.

In [11] different current conveyor based mutator implementations for converting memristor to both meminductor and memcapacitor have been proposed. Some of the implementations use a floating memristor. However only theoretical analyses are presented. Also, it is difficult to carry out these meminductor and memcapacitor mutators in practice since a reliable floating memristor emulator is necessarily required. Also the proposed circuits suffer from ii. In 2014 Liang et al. presented a practical floating memristorless meminductor emulator circuit, using simple and inexpensive off-the-shelf components like four CCII+s, two operational OPAMPs, single analog multiplier, and several passive components in [16]. The proposed mutator circuit suffers from all of drawbacks mentioned above (i,ii,iii and iv). Also in simulations commercially available active devices CA3080 and AD844 have been utilized instead of CMOS based OTA and CCII, respectively and simulations have not been done at transistor levels.

It is very important to observe that all of the above mutator simulators/emulators can only serve one purpose namely, that of behaving like a 2-port mutator for mutating one circuit element to a memstor. The 4-port metamutator used in this thesis, besides behaving like a mutator, is a multi-purpose device that can be used in realizing/simulating/emulating many electronic devices such as Universal Filters, Transconductance/Transimpedance Amplifiers, Oscillators, Rectifiers and many more.

#### 1.3 Generalized 4-Port Mutators: Metamutators

The first hard-realization shown in Figure 1.4 of memristor using a highly complex mutator circuit was introduced in [1]. Since then different types of much simpler mutator circuits have been proposed for realizing memristors using nonlinear resistors or memstors from memristor which were briefly described in Section 1.2.

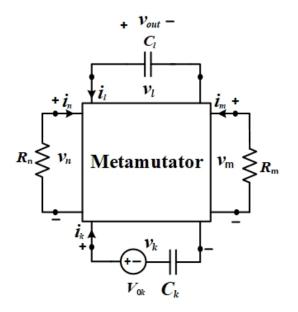

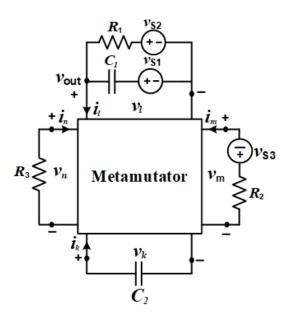

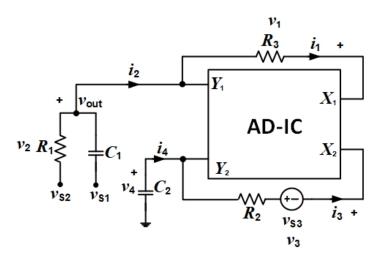

The idea of a multi-functional 4-port mutator was first introduced in [4], then under the name of "Generalized Mutative 4-port" in [25] and then named as "Metamutator" because of its ability to implement a variety of elements/systems like memstors\*, mutators, trans-admittance/trans-impedance amplifiers, multifunctional universal filters, quadrature oscillators, inverters, gyrators, multipliers etc. when some of its ports are properly terminated. Several IC designs of metamutators have been proposed and discussed in [12-14] and [24-26]. The general schematic block diagram of a metamutator is shown in Figure 1.4.

Figure 1.4: Block diagram of metamutator

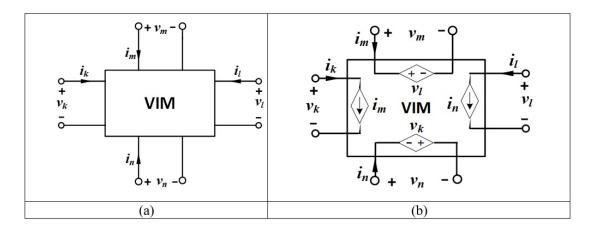

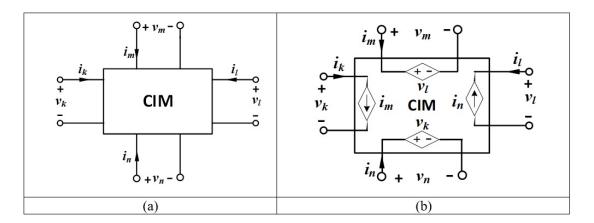

According to the minus sign in the voltage or current in one of the ports, the class of metamutators can be separated into two sub-classes:

- 1. Voltage Inverting Metamutators (VIM)

- 2. Current Inverting Metamutators (CIM)

The 4-port block diagrams of VIM and CIM are shown in Figure 1.5 and Figure 1.6 and their mathematical port descriptions are defined via the equalities (1.9) and (1.10) respectively. Although identity matrices show in both expressions in VIM a port voltage is being inverted whereas, in CIM a port current is being inverted.

$$\begin{bmatrix} i_k \\ i_l \\ v_m \\ v_n \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \times \begin{bmatrix} i_m \\ i_n \\ v_l \\ -v_k \end{bmatrix}$$

(1.9)

Figure 1.5: (a) Block diagram, (b) Circuit level realization of VIM 4-port metamutator

Figure 1.6: (a) Block diagram, (b) Circuit level realization of CIM 4-port metamutator

$$\begin{bmatrix} i_k \\ i_l \\ v_m \\ v_n \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \times \begin{bmatrix} i_m \\ -i_n \\ v_l \\ v_k \end{bmatrix}$$

(1.10)

In (1.9) and (1.10) attention should be paid to port voltages' and port currents' reference directions; due to the – sign for the voltage  $v_k$  in (1.9) and the – sign for the current  $i_n$  in (1.10). Care must be exercised in the implementation phase as to which variable follows the other in (1.9) and (1.10); variables have been indexed with letters k, l, m, n taking different values from the set {1,2,3,4}.

These metamutators all share the same port descriptions hence possess the common property of becoming a different X-Y type mutator depending on how two of the ports are terminated. This in turn makes possible, via so created mutators, of mutating classical circuit elements to memstors or memstors to memstors. All of these terminations and mutations are listed in Table 1.3.

| #  | <b>Port</b> $k$ | <b>Port</b> $m$ | Port $l$    | Port $n$    | Out  | Element      |

|----|-----------------|-----------------|-------------|-------------|------|--------------|

|    |                 |                 |             |             | put  |              |

|    |                 |                 |             |             | Port |              |

| 1  | Resistor        | Capacitor       | Memristor   | -           | n    | Meminductor  |

| 2  | Capacitor       | Resistor        | -           | Memristor   | l    | Meminductor  |

| 3  | Memristor       | -               | Resistor    | Capacitor   | m    | Meminductor  |

| 4  | -               | Memristor       | Capacitor   | Resistor    | k    | Meminductor  |

| 5  | Memristor       | Inductor        | Resistor    | -           | n    | Memcapacitor |

| 6  | Inductor        | Memristor       | -           | Resistor    | l    | Memcapacitor |

| 7  | Resistor        | -               | Memristor   | Inductor    | m    | Memcapacitor |

| 8  | -               | Resistor        | Inductor    | Memeristor  | k    | Memcapacitor |

| 9  | Capacitor       | -               | Inductor    | NL Resistor | m    | Memristor    |

| 10 | NL Resistor     | Inductor        | -           | Capacitor   | l    | Memristor    |

| 11 | -               | Capacitor       | NL Resistor | Inductor    | k    | Memristor    |

| 12 | Inductor        | NL Resistor     | Capacitor   | -           | n    | Memristor    |

TABLE 1.3: Mutation table for realizing 1-port elements [4].

#### 1.4 Thesis Outline

In the first chapter of this thesis a brief introduction to basic circuit elements together with a new class of memory elements namely, memstors have been presented. In the same chapter, the necessity of using mutators and previously developed mutator circuits in the literature have been studied. Also a brief introduction to 4-port metamutators, their classification, according to their port description matrices, into two categories, Voltage Inverting Metamutator (VIM) and Current Inverting Metamutator (CIM) have been presented.

In the second chapter the necessity of using mutators and the basic definition of 2-port mutators with their ports relation matrices and the mutators themselves for mutating nonlinear circuit elements to memristors or converting memristors to other non-volatile circuit elements like meminductor and memcapacitor have been presented also some of the previously developed classical mutator circuits, well-known in the literature, have been investigated.

In the literature there are many incognito 4-port mutator structures embedded in electronic circuits such as simulators/emulators. Nobody has been able to identify these underlying 4-ports and their ability to act as a Metamutator. With the third chapter in addition to introducing some of these incognito metamutator realizations, newly designed metamutator circuits, with one or two active devices in their structures, have been presented. Also, a novel realization of metamutator with a new single active device, Additive and Differential IC (AD-IC) along with the implementation of AD-IC with twelve transistors, has been proposed.

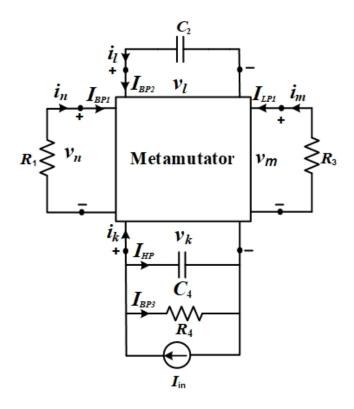

In the fourth chapter, different applications of metamutators developed during the research period of this thesis have been presented. As the port description matrix of all introduced metamutators in Chapter 3 are the same, all of these applications stand true for all of metamutators. Depending on how some of the ports are terminated, metamutator applications, can be classified in two groups, as follows:

- I. 1-port circuits realized with metamutators,

- II. 2-port circuits realized with metamutators.

For example, in 1-port realizations, by properly terminating three ports of the metamutator the resulting circuit may behave as mutator, floating and/or grounded impedance scalor, RC- oscillator. On the other hand, in 2-port realizations, by properly terminating two ports of the metamutator the resulting circuit may behave like a transconductance amplifier, transimpedance amplifier, voltage or current mode multiple input single output universal filter and single input multiple output universal filter. All of these applications have been presented in

Section 4.2 and examined in detail with PSPICE simulations using transistor parameters obtained from layout level descriptions of metamutators; comparison of simulation and theoretical results have also been presented in the same section.

In the fifth chapter of this thesis a voltage multiplier with single AD-IC and two squarer circuits in its structure and a full-wave rectifier again with an AD-IC and two diodes in its configuration have been presented. Both of the circuits were simulated with parameters extracted from the layout and simulation results show very good conformity with desired voltage multiplier and full-wave rectifier behaviors. Also a comparison of the proposed analog multiplier and full-wave rectifier with others, existing in the literature, are included into this chapter.

Conclusions and future research directions conclude the thesis in the fifth chapter followed by a list of references and appendices containing PSPICE Netlists and other implementation programs.

### Chapter 2

### **Mutator Circuits and Memstor Simulations**

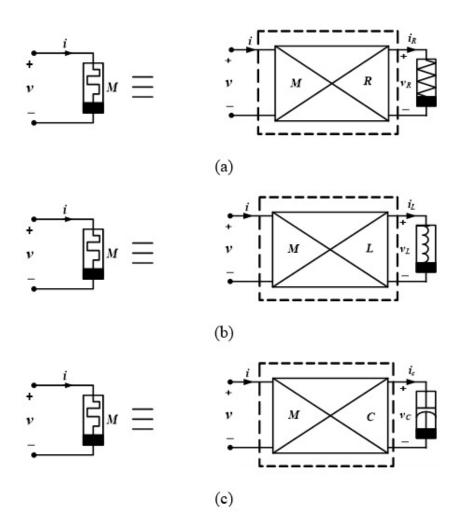

First in 1968 Leon Chua in [5] claimed that it is possible to mutate one type of circuit element, be it linear or nonlinear, into another by using a two-port mutator and he first proposed three types of mutators for mutating circuit elements to each other. In 1971, he also presented a new class of mutators, for mutating nonlinear circuit elements to memristors and vice versa [1]. According to [1] there are several types of circuit realizing the same kind of mutators which mutate element type X into element type Y, called X-Y mutator. The symbolic 2-port structures of these mutators are shown in Figure 2.1.

Figure 2.1: (a) M-R mutator (b) M-L mutator (c) M-C mutator.

The M-R, M-L, and M-C mutators which will be presented in this chapter, mutate a resistor or capacitor or inductor, all non-linear into a memristor. The basic principle of these types of mutations is preserving the "shape" of the nonlinear characteristic of the R, C and L type elements, which are mutated into the corresponding charge-flux constitutive relation of the memristor.

#### 2.1 Mutators for Mutating Nonlinear Circuit Elements to Memristor

#### 2.1.1 Mutators for Mutating Nonlinear Resistor to Memristor

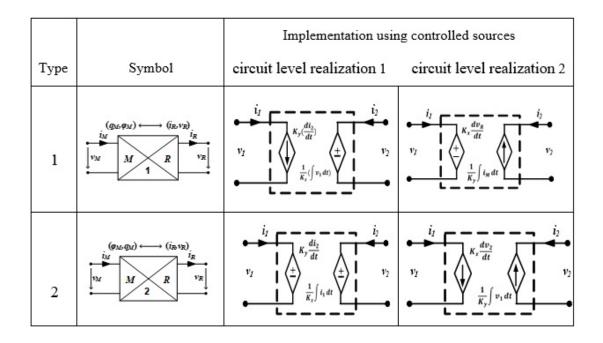

Two types and four circuit level realization for mutating nonlinear resistors to memristors are proposed by Chua as shown in Table 2.1.

TABLE 2.1: Different circuit level realizations of M-R mutator.

Both type of mutators convert voltage-current characteristic of the nonlinear resistor at port 2 to that of a memristor with same characteristic at port 1 but with a minor difference: for Type-1  $v_R$ - $i_R$  characteristic is mutated to a  $\varphi_M$ - $q_M$ characteristic whereas for Type-2 to that of a  $q_M$ - $\varphi_M$  characteristic.

General definitions of time-invariant nonlinear resistor and memristor are given in (2.1) and (2.2),

$$f_R(v_R, i_R) = 0 (2.1)$$

where  $v_R$ ,  $i_R$  are the voltage and the current of the nonlinear resistor,

$$f_{MR}(\varphi_M, q_M) = 0 \tag{2.2}$$

where  $q_M$ ,  $\varphi_M$  are the electric charge and flux of the memristor respectively.

In type one, the similarity of characteristics (2.1) and (2.2) can be observed by a linear transformation (a scaling to be more precise) of the coordinates as in (2.3).

$$\begin{cases} q_M = K_y . i_R \\ \varphi_M = K_x . v_R \end{cases}$$

(2.3)

In type two, the similarity of characteristics (2.1) and (2.2) can be observed by linear transformations of the coordinates as in (2.4).

$$\begin{cases} q_M = K_x . v_R \\ \varphi_M = K_y . i_R \end{cases}$$

(2.4)

where  $K_x$  and  $K_y$  are real constants with values depending on how the mutator is designed.

The first nonlinear resistor to memristor mutator circuit is shown in Figure 2.2. The M-R mutator of type 1, circuit level realization 1, was selected in [1]. In the circuit implementation of this mutator two operational amplifiers, 14 transistors, and a number of passive components were employed.

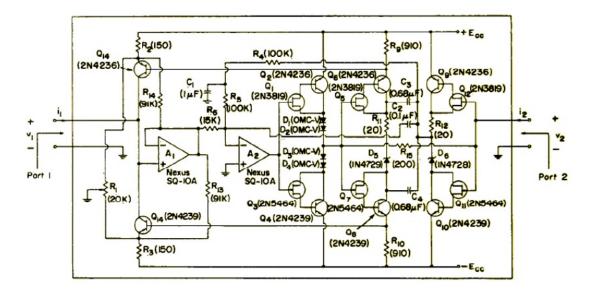

Figure 2.2: The proposed memristor emulator circuit by L.Chua [1].

In 2011 Biolek and Biolkova, by using off-the-shelf components like one Operational Amplifier (OpAmp) and two Current Feedback Operational Amplifiers (CFOA), and several passive elements introduced a mutator circuit shown in Figure 2.3 for mutating nonlinear resistors into memristors [10].

Figure 2.3: Implementation of M-R mutator with two CFOAs and one OpAmp

In 2014 a grounded memristor emulator circuit including three CFOAs, two resistors, two capacitors and one nonlinear resistor was presented in [110]. The circuit structure is shown in Figure 2.4.

Figure 2.4: Circuit structure of grounded memristor emulator in [110]

## 2.1.2 Mutators for Mutating Nonlinear-Inductor to Memristor

Two types and six circuit level realizations for mutating nonlinear inductor to memristor are proposed by Chua in [1], as shown in Table 2.2.

Both type of mutators convert  $\varphi_L - i_L$  characteristic of the time-invariant nonlinearinductor at port two to that of a memristor with same characteristic at port one

TABLE 2.2: Two types and six circuit level realizations of M-L mutators.

but with a minor difference: for Type-1  $\varphi_L - i_L$  characteristic is mutated to a  $\varphi_M - q_M$  whereas for Type-2 to that of a  $q_M - \varphi_M$  characteristic.

In the sequel some generalized 4-ports will be so designed that both types of mutators can be obtained with proper termination of two of the ports.

General definitions of time-invariant nonlinear-inductor and memristor are given with:

$$f_L(i_L,\varphi_L) = 0 \tag{2.5}$$

where  $i_L$ ,  $\varphi_L$  are current and flux of the nonlinear-inductor respectively.

$$f_{MR}(q_M,\varphi_M) = 0 \tag{2.6}$$

where  $q_M - \varphi_M$  are charge and flux of the memristor respectively.

In type one, the similarity of characteristics (2.5) and (2.6) can be observed by linear transformations of the coordinates as in (2.7).

$$\begin{cases} \varphi_L = K_x . \varphi_M \\ i_L = K_y . q_M \end{cases}$$

(2.7)

In type two, the similarity of characteristics (2.5) and (2.6) can be observed by linear transformations of the coordinates as in (2.8).

$$\begin{cases} \varphi_L = K_x . q_M \\ i_L = K_y . \varphi_M \end{cases}$$

(2.8)

where  $K_x$  and  $K_y$  are real constants with values depending on how the mutator is designed.

## 2.1.3 Mutators for Mutating Nonlinear-Capacitor to Memristor

Two types and six circuit level realizations for mutating a time-invariant nonlinearcapacitor to a memristor proposed by Chua in [1] are shown in Table 2.3.

Both type of mutators convert the  $q_C \cdot v_C$  characteristic of the time-invariant nonlinear-capacitor at port two to that of a memristor with the same characteristic at port one but with a minor difference: for Type-1  $q_C \cdot v_C$  characteristic is mutated to a  $q_M \cdot \varphi_M$  whereas for Type-2 to that of a  $\varphi_M \cdot q_M$  characteristic. In the sequel a generalized mutative 4-port will be so designed that all types of mutators can be obtained with proper termination of two of the ports.

General definitions of nonlinear-capacitor and memristor are given with (2.9) and (2.10) respectively.

TABLE 2.3: Two types and six circuit level realizations of M-C mutators.

$$f_C(q_C, v_C) = 0$$

(2.9)

where  $q_C$ ,  $v_C$  are the charge and voltage of the nonlinear-capacitor respectively.

$$f_{MR}(q_M,\varphi_M) = 0 \tag{2.10}$$

where  $q_M$ ,  $\varphi_M$  are the charge and the flux of the memristor.

In type one, the similarity of characteristics (2.9) and (2.10) can be observed by linear transformations of the coordinates as in (2.11).

$$\begin{cases} q_M = K_x . q_C \\ \varphi_M = K_y . v_C \end{cases}$$

(2.11)

In type two, the similarity of characteristics (2.9) and (2.10) can be observed by linear transformations of the coordinates as in (2.12)

$$\begin{cases} q_M = K_x . v_C \\ \varphi_M = K_y . q_C \end{cases}$$

(2.12)

where  $K_x$  and  $K_y$  are real constants with values depending on how the mutator is designed.

#### 2.2 Mutators for Mutating Memristor to Other Memstors

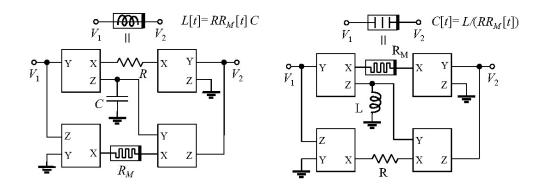

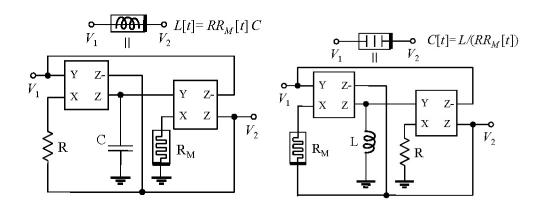

Biolek et al. in 2010, inspired by Chua's mutator circuits, proposed two classes of mutators for mutating memristor to meminductor and memristor to memcapacitor [9]. Each of these classes has two types and four circuit level realizations.

### 2.2.1 Mutators for Mutating Memristor to Meminductor

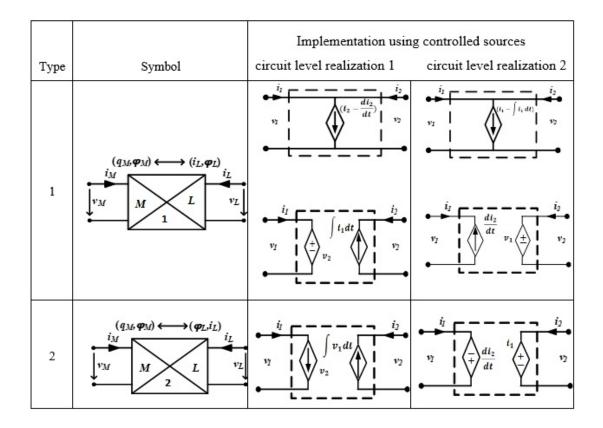

The circuit level realizations of ML-MR mutator which are extracted from [9], are illustrated in Table 2.4.

Both type of mutators convert  $q_M$ ,  $\varphi_M$  characteristic of the memristor at port two to that of a meminductor with the same characteristic at port one but with a minor difference: for Type-1  $q_M$ ,  $\varphi_M$  characteristic is mutated to a  $\rho_L$ - $q_L$  characteristic whereas for Type-2 to that of a  $q_L$ - $\rho_L$  characteristic.

General definitions of memristor and meminductor are given as:

$$f_{MR}(q_M,\varphi_M) = 0 \tag{2.13}$$

where  $\varphi_M - q_M$  are the charge and flux of the memristor respectively.

| Туре | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Circuit level realization 1                                                                                                                                                       | Circuit level realization 2                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|